Context

Our customer had a product that produces high volumes of high-speed serial data and their PC based test system was losing packets in transit. The customer needed an external device designed to interface with the equipment and to buffer the data to the PC to be sure that no packets were being dropped.

Solution

In order to meet the customers requirements, BCA leveraged a Xilinx Zynq chipset with a combined ARM processor and FPGA to receive the various serial data streams in the FPGA and buffer it using the ARM processor cores. BCA utilized the Vivado tool chain to develop a custom FPGA serial IP block to keep up with the data stream as the Xilinx provided block was not fast enough.

Though BCA is very comfortable with Linux we chose a bare metal approach for coding on the ARM processor for this particular project after evaluating Linux, a RTOS, or bare metal.

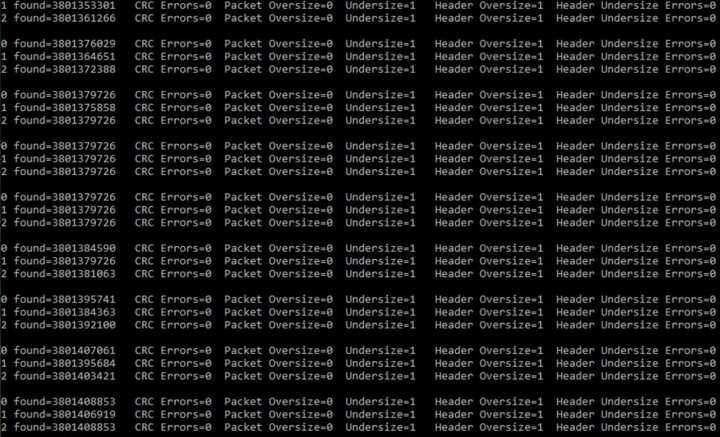

The final system was able to buffer and transmit 3 simultaneous high-speed data streams without loss over a 24-hour period.